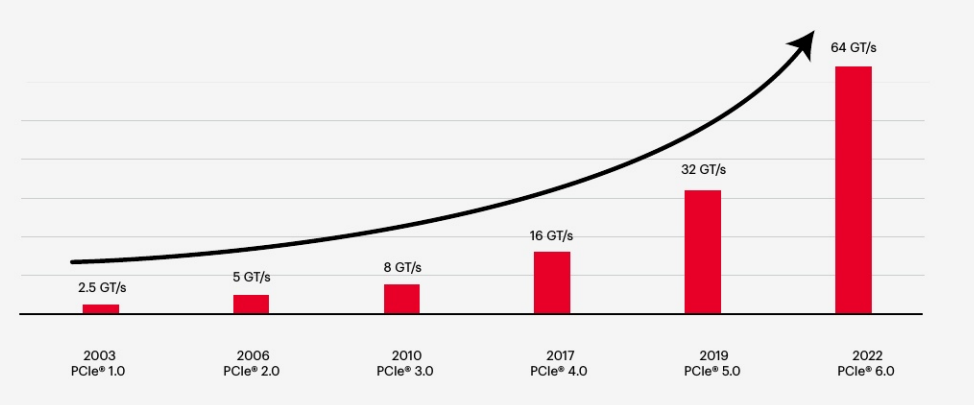

自2003年推出以來,PCIe發展至今已經從最初的1.0升級到了6.0,在之前的文章中為大家介紹了PCIe基礎知識,本文則為大家簡單介紹一下PCIe標準的演進歷史以及各代PCIe標準之間的差異。

PCIe 3.0

PCIe 2.0的傳輸速率為5 GT/s,但由于8b/10b編碼方案的開銷占比為20%,因此單lane的傳輸帶寬為4 Gb/s。PCIe 3.0及以后的版本使用更高效的128b/130b編碼,將開銷占比降低到了1.5%。

通過減少開銷占比,PCIe3.0的單lane傳輸帶寬相比PCIe2.0翻倍,達到8 Gb/s,同時保持了與PCle 2.0版本軟件和機械接口的兼容性。由于完全向下兼容,PCIe 3.0為客戶端和服務器配置提供了與PCIe 2.0相同的拓撲結構。

PCIe 1. x和2. x卡可以無縫地插入支持PCIe 3.0的插槽中,反之亦然,支持這些配置以協商的最高性能水平運行。PCIe 3.0規范包含了Base和CEM(卡機電)規范,其中基本規范里的電氣部分定義了集成電路(IC)級的電氣性能,并支持8 GT/s信令。

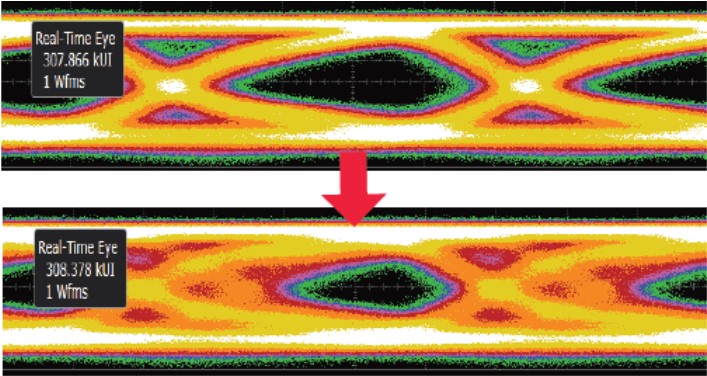

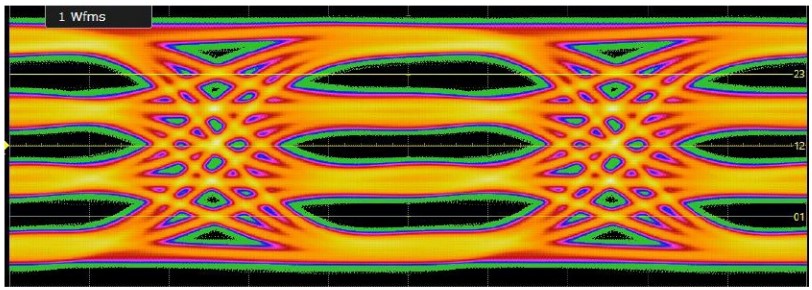

眼圖(Eye Diagram)是一種通信領域中常用的時域分析工具,它可以用來評估數字通信系統中的信號完整性和傳輸質量(因為示波器顯示的圖形很像人的眼睛,因此被稱為“眼圖”)。由于PCIe的傳輸速率隨著標準的迭代而增加,信號質量也會受到影響。如下圖中的眼圖閉合所示,通道長度越長信號質量也會越低,隨著速度和信道距離的增加,物理層的驗證測試更具挑戰性。PCIe 3.0中8 GT/s的速度嚴重降低了接收器的信號,這將在示波器上以眼圖閉合的形式出現(不均衡)。為了實現準確的通信,發送端和接收端需要就構成1和0的電平達成均衡,并采用諸如均衡和去加重等技術,使接收端清晰地看到數據。

PCIe 3.0標準增加了接收器均衡和發送器去加重點,這對于能否實現8 GT/s及以上的速率至關重要。均衡可以在發送器、接收器或同時在兩者中。PCIe 1.x和PCIe 2.x指定了一種簡單的均衡形式,稱為發送器去加重。去加重減少了接收器接收到的低頻能量,均衡則降低了高頻時更大的信道損耗影響。

接收器均衡的實現需要各種類型的算法,最常見的兩種是線性反饋和決策反饋(DFE)。發送器去加重均衡發生在發送器,而DFE預加重發生在接收器。接收器均衡也可以包括與DFE相結合的連續時間線性均衡(CTLE)。

為了提高發送端和接收端之間的傳輸距離,PCIe 3.0引入了一個主動均衡適應過程,接收器可以調整發送器的前置尖頭信號和去加重,以實現最適合自己的特定傳輸線的均衡性能。該性能需要全新的物理層測試,即接收器和發送器的鏈路均衡測試。鏈路均衡接收器測試的目的是檢查接收器是否可以在最壞的應力條件下調整其鏈路的發送器均衡,而鏈路均衡發送器測試的目的是檢查發送器是否按照鏈路的接收器的請求在物理上和邏輯上執行更改。

PCIe 4.0

PCIe 4.0標準在PCIe 3.0上線7年后于2017年推出。與前一代相比,PCIe 4.0將傳輸速率從8 Gb/s提高至16 Gb/s,并與前幾代技術從軟件到時鐘架構再到機械接口充分兼容。

從協議和編碼的角度來看,PCIe 4.0與PCIe 3.0有許多共同點,包括128/130位編碼。乍一看,PCIe 4.0與PCIe 3.0的共同點相較PCIe 3.0與PCIe 2.0的共同點更多。但是,當提高設備速度時,會自動通過相同的通道發送更高的頻率。電信號傳輸過程中鏈路中的電阻會導致插入損耗或衰減,并隨著頻率的提高而增加。

在16 GT/s時,PCIe 4.0信號在典型的FR4通道(最常見的印刷電路板材料)中衰減顯著。因此,為確保PCIe 4.0設計的信號完整性需要額外的測試,原因是16GT/s(PCIe 4.0)的信號損失比8 GT/s(PCIe 3.0)的信號損失要大得多。PCIe 4.0在規范中增加了計時器部分以擴展通道的范圍,并特別增加了系統的復雜性測試。

即使測試復雜度增加,8 GT/s的PCIe 3.0測試次數也高于16 GT/s的PCIe 4.0測試次數。這是因為PCIe 3.0需要測試三種不同的通道場景:即短、中、長,而PCIe 4.0僅測試長通道場景即可。

與PCIe 3.0一樣,PCIe 4.0有時也被稱為“閉眼”規范。這意味著即使你有一個完美的發送器,以及一個基本零抖動的發送器,當你把發送器連接到一個頻道時,符號間的干擾會迫使“眼睛”閉上。能否成功傳輸PCIe 4.0信號,取決于接收器的均衡策略能否將“眼睛”打開。

當支持16 GT/s的PCIe 4.0設備鏈接到另一個支持16 GT/s的PCIe 4.0設備時,鏈路均衡有兩個步驟。首先,以8 GT/s的速度建立鏈接,如果成功,鏈路均衡過程將再重復一次,以達到16 GT/s的速率。

對于PCIe 4.0,設計人員應該評估其系統的性能變化耐受度。了解性能變化是必不可少的,因為信號性能因卡而異。這些差異會導致信道損耗、串擾和信道不連貫的增加,從而導致更多的系統噪聲、抖動性能的惡化和信號閉眼。

PCIe 5.0

PCI-SIG于2019年5月發布了PCIe 5.0規范,將傳輸速率提高一倍,達到32 GT/s,同時保持低功耗和與前幾代的向后兼容性。PCIe 5.0承諾通過x16配置達到128 GB/s的吞吐量,在數據中心可實現400GE的速度。

PCIe 5.0和400GE的速度共同支持人工智能(AI)、機器學習、游戲、視覺計算、存儲和網絡等應用。這些進步使5G、云計算和超大規模數據中心的創新得以推動。

PCIe 5.0標準是在4.0的基礎上做了一個相對簡單的擴展。它采用與PCIe 4.0相同的Tx和Rx測試方法,以及類似用于校準接收器應力抖動測試的“眼睛”寬度和高度的方法。新標準進一步降低了延遲,并兼容了長距離應用的信號損失。PCIe 5.0使用128b/130b編碼方案,該方案在PCIe 3.0和兼容的CEM連接器中首次亮相。

PCIe 5.0中的新功能是均衡旁路模式,能實現從2.5 GT/s直接到32 GT/s的訓練,可加快鏈路初始化速度,這有助于在發送器、信道和接收器條件的系統(如嵌入式系統)中減少鏈路啟動時間,為32 GT/s的鏈路均衡測試提供了一條新的訓練路徑。

一般來說,除了需要實現速度提升,或者實現電氣更改以提高信號完整性和連接器的機械強度之外,規格變化很小。

PCIe 6.0

PCI-SIG于2022年1月發布了PCIe 6.0規范。PCIe 6.0技術是第一個使用脈沖幅度調制4級(PAM4)信號編碼的PCI Express標準,使PCIe 6.0設備在保持相同信道帶寬的情況下能實現PCIe 5.0設備兩倍的吞吐量。PCIe 6.0技術最高可達64 GT/s,同時保持低功耗和向后兼容。PCIe 6.0承諾通過x16配置達到256GB/s的吞吐量,在數據中心實現800GE速度。

PCIe 6.0和800GE的速度共同支持AI、機器學習、游戲、視覺計算、存儲和網絡等應用,以推動5G、云計算、超大規模數據中心等領域的發展。

PCIe 6.0采用高階調制格式PAM4信號,是對PCIe 5.0技術的重大升級。但是,它對Tx和Rx測試使用了相同的高級方法,同時添加了一些特定于PAM4的新發射器測量編碼。與前幾代類似,PCIe 6.0設備采用64 GT/s操作的發送器和接收器均衡,并要求前向糾錯(FEC)。

除了這些電氣變化之外,PCIe 6.0還引入了流量控制單元(FLIT)編碼。與物理層的PAM4不同,FLIT編碼用于邏輯層,將數據分解為固定大小的數據包。PCIe 6.0以FLIT為單位進行事務傳輸,每個FLIT有256 B數據(1 FLIT=236B TLP+6B DLP+8B CRC+6B FEC=256B),每B數據占用4 UI。此外,FLIT編碼還消除了以前PCIe規范的128B/130B編碼和DLLP(數據鏈路層數據包)開銷,從而顯著提高了TLP(事務層數據包)效率。

雖然PCIe 6.0更具優勢,并且已經提出一年有余,但在PCIe 5.0還沒有完全普及的當下,PCIe 6.0何時才能走進用戶,有著諸多的不確定因素。目前來看,高性能和吞吐量的應用程序更需要PCIe 6.0,例如包括用于AI工作負載的圖形處理單元、高吞吐量網絡應用程序和Compute Express Link (CXL)技術,成為異構計算架構下數據交互的高速公路。

PCIe 6.0接口在保持對前幾代產品的向后兼容性的同時,將傳輸速率提高了一倍,達到64 GT/s,在相同的最大16通道下提供256 GB/s的吞吐量。而7.0版的PCIe規范,將于2025 年發布,預計數據傳輸速率將再次翻倍,達到128Gbps。

內容來源:

*Evolution-of-PCIe-Standards-and-Test-Requirements

地址:深圳市南山區記憶科技后海中心B座19樓

電話:0755-2681 3300

郵箱:support@unionmem.com